기술분야: 응용물리학과

보유기관:

연구자: 김보성

기술완성도 TRL4

| 기술분야: 응용물리학과 | 보유기관:  |

| 연구자: 김보성 | |

|

기술완성도

TRL1

TRL2

TRL3

TRL4

TRL5

TRL6

TRL7

TRL8

TRL9

|

|

기술 상담 후 협의

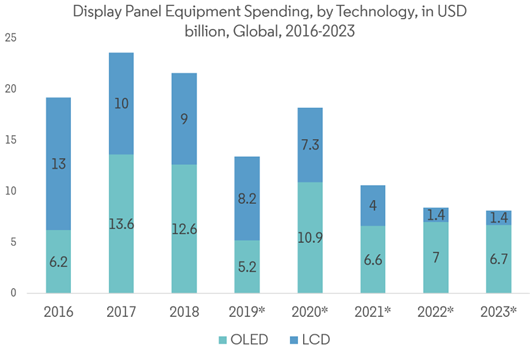

본 기술의 박막 트랜지스터는 LCD, OLED와 같은 액티브 매트릭스 디스플레이 패널의 핵심 부품으로 휴대폰, 노트북, 모니터, TV 등 다양한 전자 디스플레이 제품에 사용됨

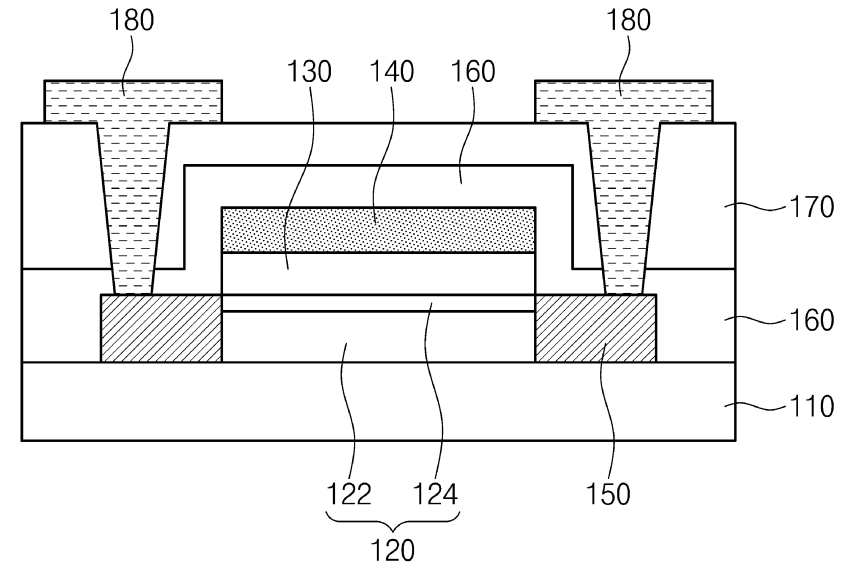

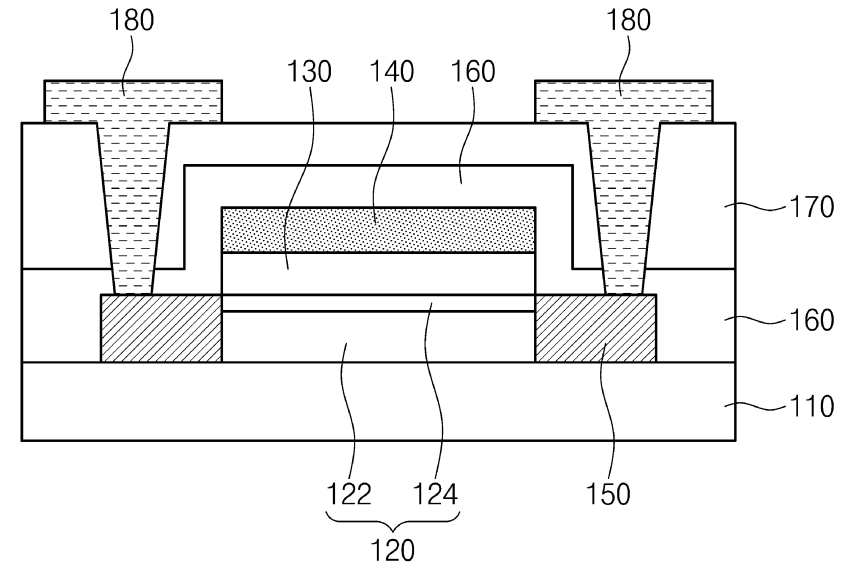

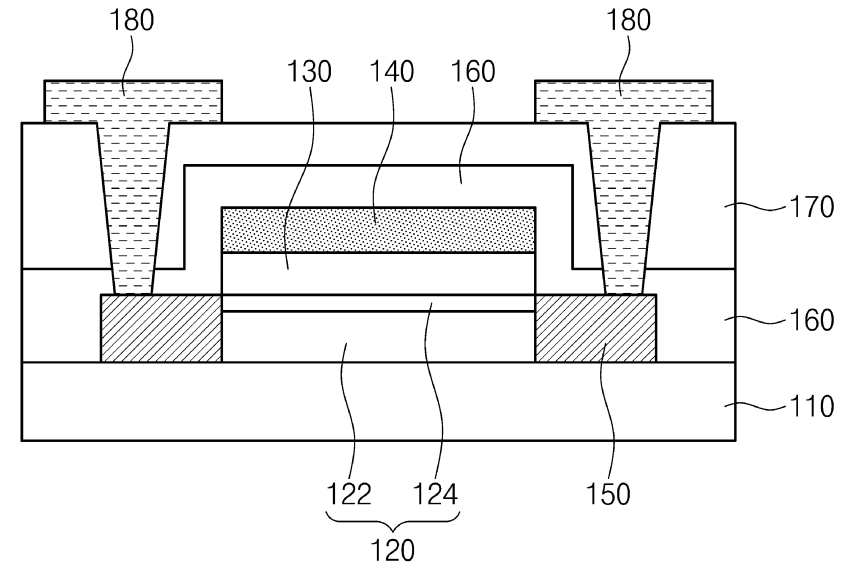

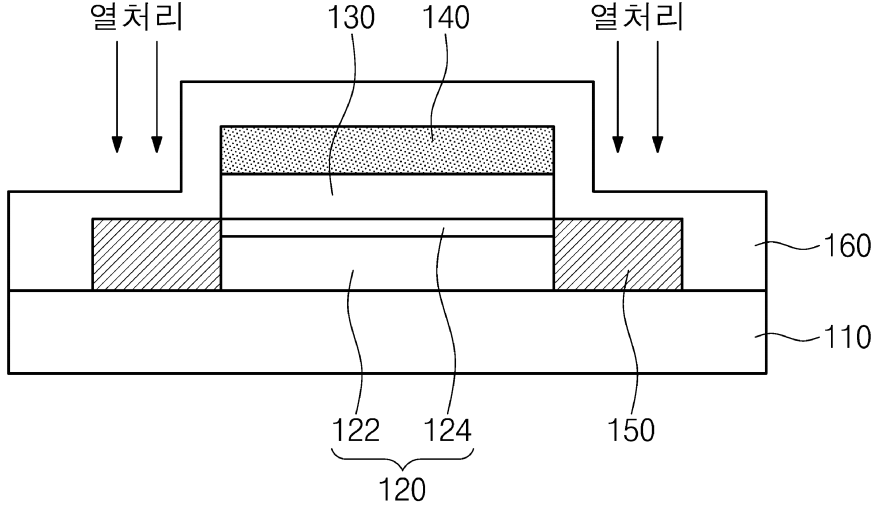

박막 트랜지스터 및 그 제조 방법에 관한 것으로, 보다 상세하게는, 이중 반도체 층을 포함하는 박막 트랜지스터 및 그 제조 방법임

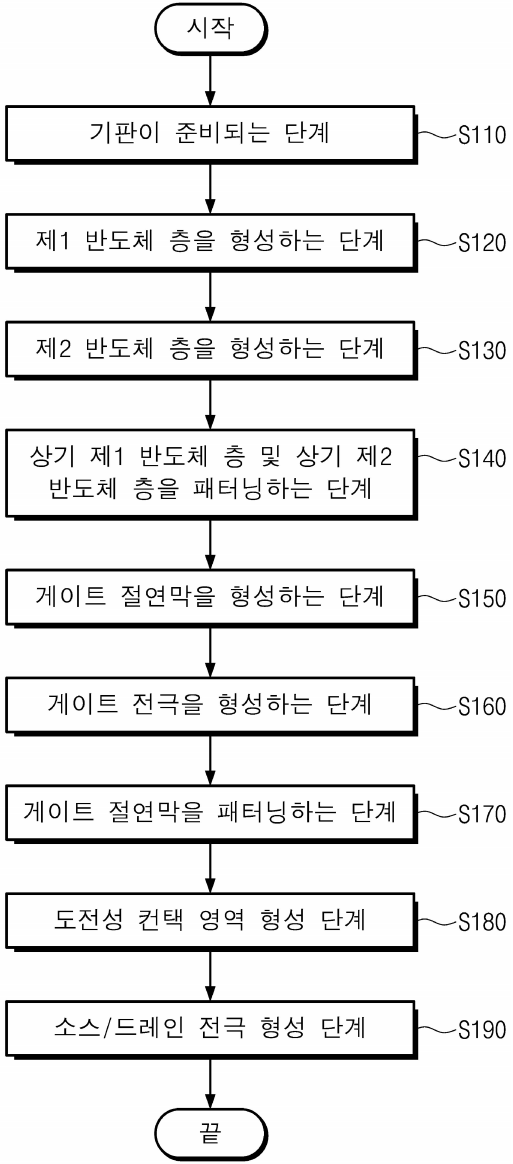

제조 방법은 기판이 준비되는 단계부터 소스/드레인 전극 형성 단계까지 총 9단계로 구분됨

박막 트랜지스터 제조공정의 높은 복잡성

박막 트랜지스터 제조공정의 낮은 경제성

본 기술의 과제는 4가지로 이중층 구조의 반도체 층을 갖는 박막 트랜지스터의 제조 방법을 제공, on/off ratio가 향상된 박막 트랜지스터를 제공, 전기적 특성이 향상된 박막 트랜지스터를 제공, 신뢰성 및 안정성이 향상된 박막 트랜지스터를 제공 등이 있음

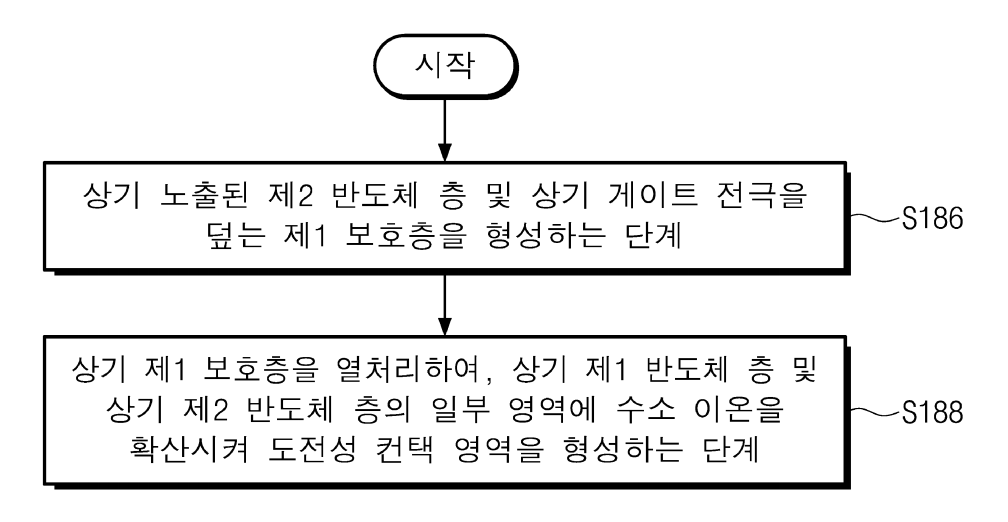

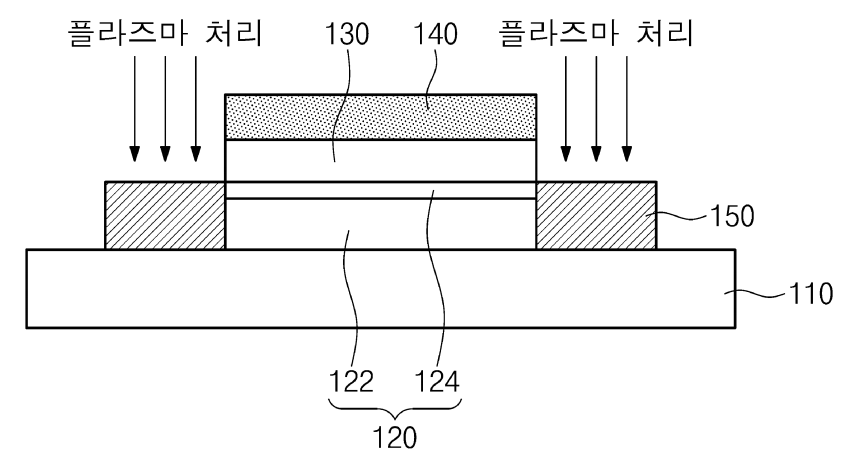

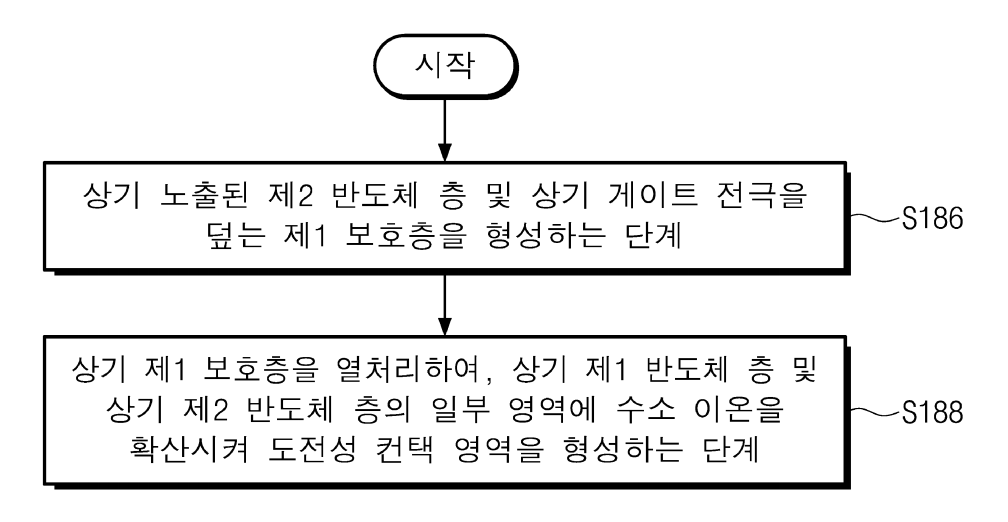

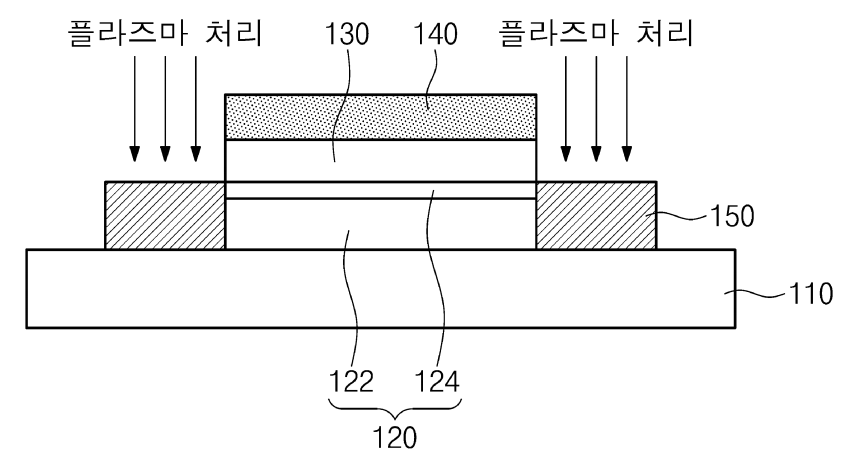

기술적 과제를 해결하기 위해 박막 트랜지스터의 제조방법은 총 9단계로서 단계적 특성을 제공

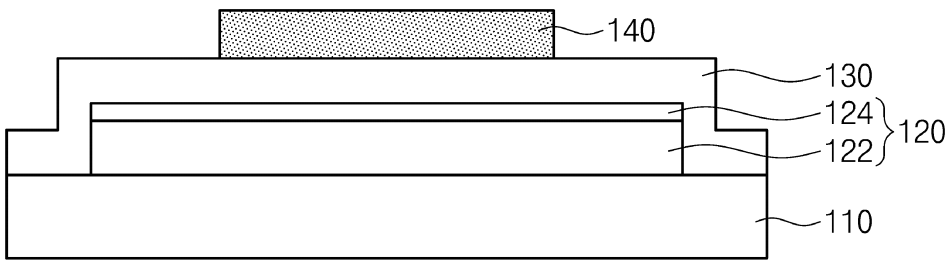

본 기술의 실시 예에 따른 박막 트랜지스터의 제조 방법은, 기판 상에 제1 반도체 층을 형성하고, 상기 제1 반도체 층 상에 제2 반도체 층을 형성하고, 상기 제1 반도체 층 및 상기 제2 반도체 층을 동시에 패터닝이 형성되고 이에 따라, 박막 트랜지스터의 제조 공정이 간소화되어, 공정의 경제성이 향상됨

또한, 본 발명의 실시 예에 따른 박막 트랜지스터는 제1 반도체 층 및 상기 제1 반도체 층보다 얇은 두께를 갖는 제2 반도체 층을 포함하는 반도체 층을 갖고, 상기 반도체 층의 일부가 변경된 도전성 컨택 영역을 형성되고 이에 따라, 상기 도전성 컨택 영역이 상기 제2 반도체 층과 전기적으로 접촉하여, 박막 트랜지스터의 전기적 특성이 향상됨

박막 트랜지스터(TFT) 기술은 LCD 또는 OLED와 같은 액티브 매트릭스(active matrix) 디스플레이 패널의 핵심 부품으로 휴대폰, 노트북, 모니터, TV 등 다양한 전자 디스플레이 제품에 활용됨

박막 트랜지스터 시장은 2021~2026년 동안 17.34%의 CAGR을 기록할 것으로 예상됨

박막 트랜지스터 시장은 시장에 다수의 지배적인 플레이어가 존재하지 않아 단편화되어 있으며, 많은 기업에서는 시장에서 수익성 있는 성장 기회를 창출할 것으로 예상되는 추가 응용 프로그램을 분석하기 위해 연구 개발 활동을 업그레이드하려는 노력을 기울이고 있음

박막 트랜지스터 및 그 제조 방법

출원번호: 10-2017-0113455

출원일자: 2017년 09월 05일

특허권자: 고려대학교 세종산학협력단

발명자: 김보성, 홍문표